Applicable Model(s): HMC7000, HMC7-MI-01

Summary

The HMC7-MI-01 16 input I/O Module has built-in High Speed Counter (HSC) functionality, however, there is no built-in register to indicate that the counter has incremented past the HSC preset value. This technical note describes how to set up a ladder logic block that will set a bit when the preset is reached.

Solution

Tag Configuration:

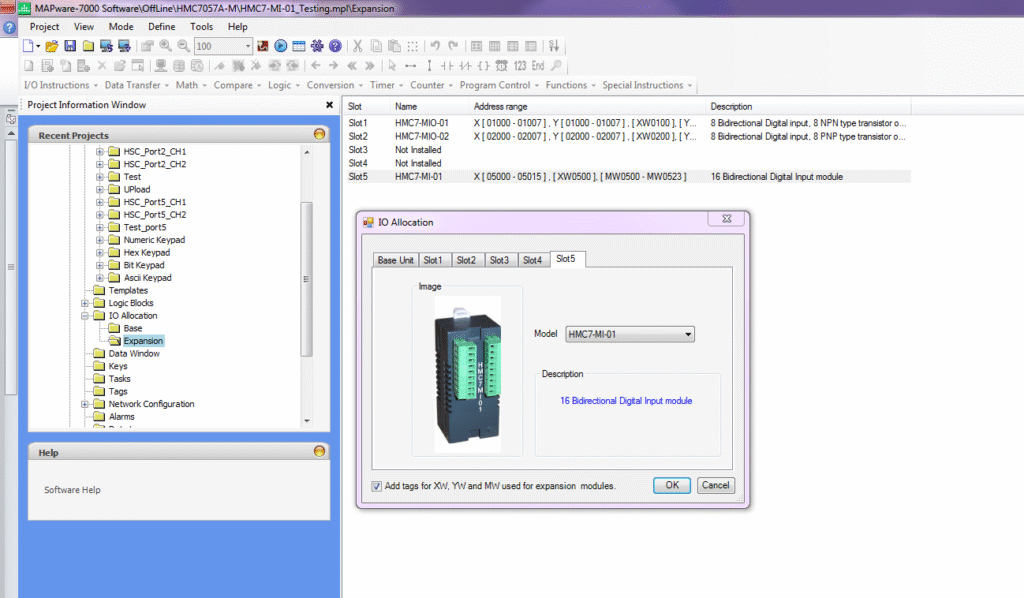

In MAPware-7000 first configure HMC7-MO-01 in Slot1 and HMC7-MO-02 in Slot2 then the relevant expansion port with the HMC7-MI-01 module. This is done from the IO Allocation –> Expansion folder of the project directory.

MAPware-7000 will automatically allocate the tags in Table 1 when the IO module is configured.

Table 1 – Tags automatically allocated when IO module is configured in port:

| Tag | Register | Function |

|---|---|---|

| HSC Enable Bit (CH1)- Slotnn* | Mnn080* | When set the HSC counter register will increment as the counter input toggles |

| HSC Reset Bit (CH1)- Slotnn* | Mnn081* | When set the HSC counter register will be set to zero |

| HSC Configuration register(CH1)-Slotnn* | MWnn000* | 0:Normal Operation, 2: HSC ** To access the HSC counter register this register must be configured with 010b = 2 in the three least significant bits |

| High Speed Counter (HSC) Register (CH1)- Slotnn* | MWnn01* | HSC current value |

| HSC Preset Register (CH1)- Slotnn* | MWnn03* | HSC preset value |

| HSC Enable Bit (CH2)- Slotnn* | Mnn176* | When set the HSC counter register will increment as the counter input toggles |

| HSC Reset Bit (CH2)- Slotnn* | Mnn177* | When set the HSC counter register will be set to zero |

| HSC Configuration register(CH2)-Slotnn* | MWnn06* | 0:Normal Operation, 2: HSC ** To access the HSC counter register this register must be configured with 010b = 2 in the three least significant bits |

| High Speed Counter (HSC) Register (CH2)- Slotnn* | MWnn07* | HSC current value |

| HSC Preset Register (CH2)- Slotnn* | MWnn09* | HSC preset value |

** See the module quick start guide for more information on configuration register settings

In addition the tags in Table 2 need to be manually configured. Tags are configured in the Tags folder of the project directory. To add a tag right click in the tag list and select add. Table 2 shows the tags configured for to enable a done bit for HSC Channel 1, to implement a done bit for HSC Channel 2 the tags will need to be duplicated with different addresses.

Table 2 – Tags manually configured to implement HSC done bit using HMC7-MI-01:

| Tag* | Register* | Function |

|---|---|---|

| HSC Counter Local (CH1)- Slotnn | D0000 | Buffer to save HSC counter register value in “D” memory |

| HSC Counter Low Word (CH1)- Slotnn | D0000 | Buffer to contain two LEAST significant bytes of the HSC COUNTER register |

| HSC Counter High Word (CH1)- Slotnn | D0001 | Buffer to contain two MOST significant bytes of the HSC COUNTER register |

| HSC Preset Local (CH1)- Slotnn | D0002 | Buffer to contain HSC Preset register value in “D” memory |

| HSC Preset Low Word (CH1)- Slotnn | D0002 | Buffer to contain two LEAST significant bytes of the HSC PRESET register |

| HSC Preset High Word (CH1)- Slotnn | D0003 | Buffer to contain two MOST significant bytes of the HSC PRESET register |

| Enable HSC Done Bit (CH1)-Slotnn | B0000 | Setting this bit enables the compare logic |

| HSC Done Bit (CH1)-Slotnn | B0001 | Bit to indicate that the low word of the counter has reached the low word of the preset |

| HSC High Word Done Bit (CH1)-Slotnn | B0002 | Bit to indicate that the high word of the counter has reached the high word of the preset |

Ladder Logic Configuration:

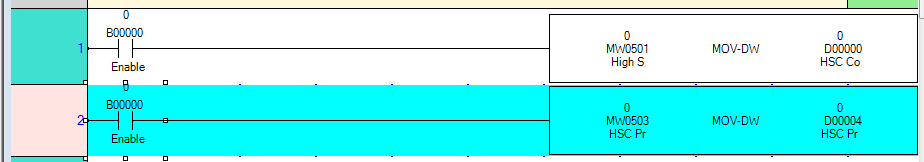

Once the tags are created a logic block can be constructed to copy the values in the 32 – bit HSC registers to internal registers, where the individual words can be compared using ladder logic instructions.

Create a new logic block by right clicking on the Main folder and selecting New Logic Block.

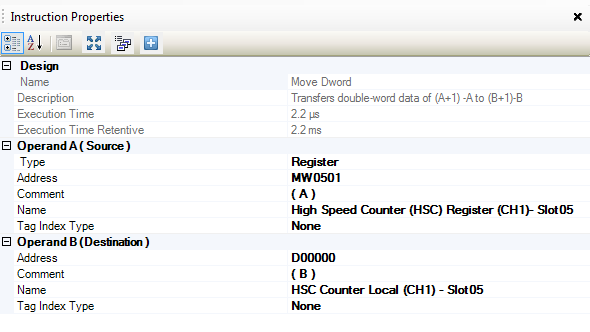

In the logic block insert two rungs and add a NO contact configured to read the Enable HSC Done Bit … in each rung. Next add a Move DW instruction to transfer the values from the High Speed Counter (HSC) Register… register and the HSC Preset Register… register to the HSC Counter Local… and HSC Preset Local… registers. Configure the built in HSC tags as the Operand A (Source) of the Move DW instructions, and the Local tags as Operand B (Destination) of the instructions. The High Word and Low Word tags will automatically be aligned to the proper word in the “Local” tags.

Next create logic to compare the individual words of the counter and preset registers. The logic must be implemented as shown in Table 3.

Table 3 Truth Table for HSC Done Bit

| Condition | Done Bit |

|---|---|

| HSC Low Word < Preset Low Word HSC High Word < Preset High Word | False |

| HSC Low Word > Preset Low Word HSC High Word < Preset High Word | False |

| HSC Low Word < Preset Low Word HSC High Word = Preset High Word | False |

| HSC Low Word >= Preset Low Word HSC High Word = Preset High Word | True |

| HSC High Word > Preset High Word | True |

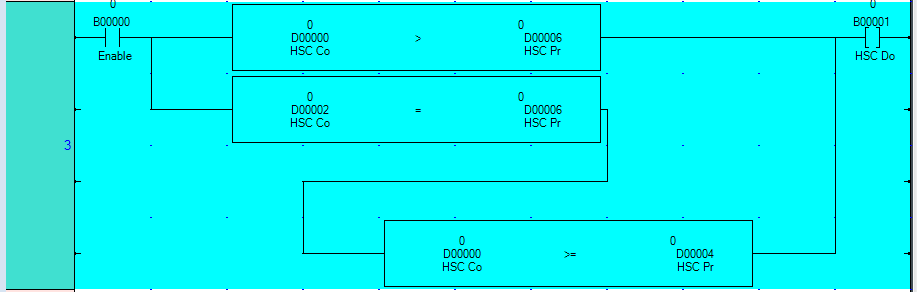

The ladder logic segment in Figure 4 implements the logic in Table 3.

This logic rung uses two branches the first branch uses a greater than instruction to set the HSC Done… bit if the high word of the counter register is greater than the high word of the preset register. This corresponds to the second True condition in Table 3. Configure Operand A with the HSC Counter High Word… tag. Configure Operand B with the HSC Preset High Word… tag.

The second branch uses two compare instructions in a series (AND) configuration. the enable bit and the HSC High Word Done … bit as normally open input conditions. Then there are two compare instructions in parallel (OR) configuration.

The first compare instruction is a Greater Than Or Equal to instruction that compares HSC Counter Low Word… (Operand A) to HSC Preset Low Word… (Operand B).

Thus if the logic is enabled AND the high word of the counter is equal to the high word of the preset register AND the low word of the counter register is greater than or equal to the low word of the preset register THEN the HSC Done Bit is set. This corresponds to the first TRUE output in Table 3.

The second compare instruction is a Greater Than instruction that is configured to be true if the HSC Counter High Word… (Operand A) is greater than HSC Preset High Word… (Operand B). This corresponds to the second true entry in Table 3.

NOTE: If the HSC counter register is incremented past 232 the register will roll over and continue counting from zero and the done bit will be cleared.